110 EEUL

## 國立臺北科技大學 110 學年度碩士班招生考試

系所組別:2152 電機工程系碩士班戊組

第一節 數位邏輯 試題 (選考)

第1頁 共2頁

## 注意事項:

- 1. 本試題共 9 題, 每題 5-25 分, 共 100 分。

- 2. 不必抄題,作答時請將試題題號及答案依照順序寫在答案卷上。

- 3. 全部答案均須在答案卷之答案欄內作答,否則不予計分。

- 1. (5%) A digital circuit has a word length of 7 bits (including sign). Assuming 2's complement is used in this circuit to represent negative numbers, what range of integers can be stored? (Express your answers in decimal.)

- 2. (10%) Simplify the following expression to the minimal sum of products (5%) and then factor the result to obtain a product of sums (5%):

$$ab'cd'e + acd + acf'gh' + abcd'e + acde' + e'h'$$

- 3. (10%) Packages arrive at the stockroom and are delivered on carts to offices and laboratories by student employees. The carts and packages are various sizes and shapes. The students are paid according to the carts used. There are five carts and the pay for their use is

- Cart C1: \$2

- Cart C2: \$1

- Cart C3: \$4

- Cart C4: \$2

- Cart C5: \$2

On a particular day, seven packages arrive, and they can be delivered using the five carts as follows:

- C1 can be used for packages P1, P3, and P4.

- C2 can be used for packages P2, P5, and P6.

- C3 can be used for packages P1, P2, P5, P6, and P7.

- C4 can be used for packages P3, P6, and P7.

- C5 can be used for packages P2 and P4.

The stockroom manager wants the packages delivered at minimum cost. Present a systematic procedure for finding the minimum cost solution.

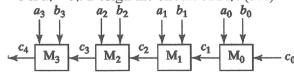

4. (10%) (a) A 4-bit Comparator is shown in the following form. The  $M_i$  are identical, and a single line connects them with information flowing from right to left. It outputs  $c_i = 0$  if  $a_i \ge b_i$  and  $c_i = 1$  if  $a_i < b_i$ . Design the circuit of  $M_i$ . (5%)

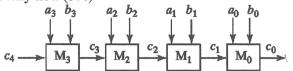

(b) Consider an alternative design where the information flow is from left to right as shown. Can the 4-bit Comparator be designed in this form? If yes, complete the design of  $M_i$ . If no, explain why not. (5%)

5. (10%) Find a minimum two-level, multiple-output AND-OR gate circuit to realize these functions.

$$f_1(a, b, c, d) = \sum m(10, 11, 12, 15) + \sum d(4, 8, 14)$$

$f_2(a, b, c, d) = \sum m(0, 4, 8, 9) + \sum d(1, 10, 12)$

$f_3(a, b, c, d) = \sum m(4, 11, 13, 14, 15) + \sum d(5, 9, 12)$

- 6. (10%) Braille is a system which allows a blind person to read alphanumerics by feeling a pattern of raised dots. Design a circuit that converts BCD to Braille. The table shows the correspondence between BCD and Braille.

- (a) Use a Programmable Logic Array. Give the PLA table. (5%)

- (b) Use a decoder and minimum number of gates. (5%)

|              | \                    |   | $\sim$ |             |       |   |

|--------------|----------------------|---|--------|-------------|-------|---|

| 7            | V                    | V |        |             |       |   |

| 1            | Z                    | 2 | D      | $C_{\perp}$ | В     | A |

| *            |                      |   | 0      | 0           | 0     | 0 |

|              | •                    |   | 1      | 0           | 0     | 0 |

|              | 8                    |   | 0      | 1           | 0     | 0 |

| 8            |                      |   | 1      | 1           | 0     | 0 |

| 0            | *                    |   | 0      | 0           | 1     | 0 |

|              | 9                    |   | 1      | 0           | 1     | 0 |

| 9            | 9 9                  |   | 0      | 1           | Amend | 0 |

| 0            | 6                    |   | 1      | 1           | 9     | 0 |

|              | 9                    |   | 0      | 0           | 0     | 1 |

| 8            | 0                    |   | 1      | 0           | 0     | 1 |

| proporteiore | <b>ренезавинение</b> |   |        |             |       |   |

- 7. (10%) An AB latch operates as follows: If A = 0 and B = 0, the latch state is Q = 0; if either A = 1 or B = 1 (but not both), the latch output does not change; and when both A = 1 and B = 1, the latch state is Q = 1.

- (a) Derive the characteristic equation for this AB latch. (5%)

- (b) Derive a circuit for the AB latch with two-input NAND gates and inverters. (5%)

- 8. (25%) A *M-F* flip-flop behaves as follows:

If MF = 01, the flip-flop remains the original state.

If MF = 11, the flip-flop is set to Q = 0.

If MF = 00, the flip-flop is set to Q = 1.

The input combination MF = 10 is not allowed.

- (a) Give the characteristic (next-state) equation for this flip-flop. (5%)

- (b) Realize a MF flip-flop using an AB latch described in the previous problem. (10%)

- (c) Design a counter using *MF* flip-flops which counts in the sequence: (10%) 000, 100, 111, 010, 011, 000, 100, . . .

注意:背面尚有試題

## 第2頁 共2頁

9. (10%) Design a Mealy sequential circuit which investigates an input sequence X and will produce an output of Z=1 for any input sequence ending in 0010 or 100. Example:

Notice that the circuit does not reset to the start state when an output of Z = 1 occurs. Design your circuit using NAND gates, NOR gates, and T flip-flops. Any solution which is minimal for your state assignment is acceptable.